Les puces en 5 nm d'IBM consommeront 4 fois moins d'énergie

IBM a dévoilé un processus de fabrication de transistors qui permettra de graver des processeurs en 5 nanomètres. Théoriquement, la consommation d'énergie peut être divisée par quatre par rapport aux puces gravées en 10 nanomètres.

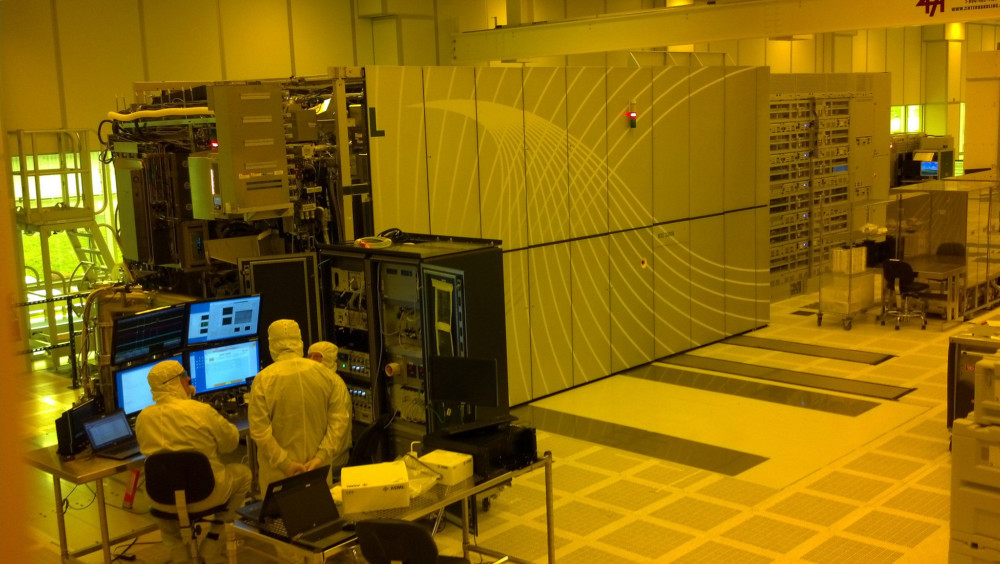

En collaboration avec Samsung et GlobalFoundries, IBM a dévoilé un procédé de fabrication pour concevoir le tout premier processeur gravé en 5 nanomètres. Et le moins que l'on puisse dire, c'est que celui-ci promet de très grosses améliorations.

De 10 à 5 nm, 4 fois moins d'énergie

Pour commencer, par rapport au 10 nm actuellement en vigueur, le nouveau procédé de fabrication en 5 nm permet de concevoir des puces 40 % plus performantes à consommation égale.

Ou bien elle permet aux processeurs de consommer 75 % d'énergie de moins à performances égales. Autrement dit, la nouvelle puce est quatre fois moins gourmande en énergie. Il est important de préciser que cela ne se traduira pas par une autonomie quatre fois meilleure, puisque le processeur n'est qu'un des composants consommant de l'énergie, mais les appareils équipés de telles puces seront néanmoins beaucoup plus endurants.

Du FinFET au GAAFET

Cette prouesse est notamment due à un procédé de fabrication innovant. IBM ne s'est pas reposés sur les transistors 3D FinFET largement utilisés aujourd'hui. En effet, ces derniers ont permis de réaliser de très gros gains de performances sur des gravures toujours plus petites. Cela justifiait donc toujours parfaitement le coût supplémentaire du FinFET.

Néanmoins, théoriquement, le FinFET ne permet plus des gains aussi impressionnants sur des gravures en dessous de 7 nanomètres. Difficile, dans ces cas-là, de justifier toutes les contraintes de production qu'engendrent les transistors FinFET.

C'est pourquoi, IBM s'est reposé sur l'évolution du FinFET : les transistors GAAFET (gate-all-around). Ces derniers sont faits d'empilements de nanofeuilles de silicium. Par le biais de cette architecture, il est possible de réaliser de grosses optimisations de performances et d'efficacité énergétique sur des gravures plus petites. Théoriquement, on peut aller jusqu'à 3 nanomètres.

Des puces gravées en 7 nanomètres devraient arriver sur le marché en 2018. Samsung investit notamment dans ce domaine et MediaTek est également intéressé. Quant aux processeurs en 5 nanomètres, il faudra sûrement attendre quelques années.